With the exponentially increasing demand for high-resolution, high-speed streaming content over the Internet, NG-PON2 based optical line terminals (OLTs) are asserting their position as key technological drivers for optical distribution networks of the future. Low production volumes and the high cost of OLTs, along with the need for implementation flexibility, make FPGAs advantageous and a popular choice for system implementation.

However, burst mode clock data recovery (BMCDR) presents a significant challenge for FPGAs at these data rates. Classical CDR and oversampling techniques used in GPON and XG-PON implementations no longer suffice for NG-PON2, owing to higher upstream data rates. So FPGAs used in these systems require transceivers that natively support burst mode receiver (BMR) functionality at 10G speeds. Until recently, FPGAs with these capabilities were too large, consumed too much power, and were prohibitively expensive for these applications. But now, the availability of cost-optimized, low-power FPGAs at mid-range densities with intrinsic BMCDR support is facilitating new ways to solve difficult OLT design challenges.

FPGAs’ role in meeting bandwidth demand

The world’s bandwidth requirement is an ever-burgeoning number driven by rapid advancements in technology and infrastructure. Adoption and distribution of 5G network infrastructure requiring a web of interlinked data centers can be ascribed as one of the major elements driving the demand for optical network equipment in the future.

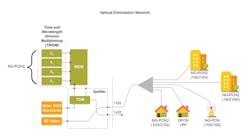

Existing GPON and XG-PON based networks provide asymmetrical upstream and downstream capacities and strive hard to provide 100-Mbps speeds, let alone scale to gigabit rates. The next generation of passive optical networks, NG-PON2, uses time- and wavelength-division multiplexing techniques to outperform its predecessors and offers backward compatibility, cost-effectiveness, and flexibility (Figure 1).

FPGAs will play a key role in delivering these capabilities. NG-PON2 institutes strict performance, flexibility, and scalability requirements for network equipment architectures, especially OLTs. FPGAs present a cost-optimized and effective platform for meeting the following OLT system development requirements:

- Flexibility. With custom programmable hardware logic and configurable memory blocks, FPGAs allow designers the luxury of building upon a low-level design to incorporate more features and functions as required. FPGA-based OLT designs are flexible and scalable and enable designers to keep pace with the current trend in technology.

- Low production volumes and high costs. OLT equipment is especially sensitive to cost, owing to low production volumes and an aggressive need to future-proof the device. These devices must accommodate power-efficient multi-port capabilities and interact seamlessly with numerous optical network unit (ONU) devices to swiftly lock data continuously (burst mode), which contributes considerably to design complexity. While ASSPs can solve such problems, they require large capital and long and complex design cycles without delivering design flexibility or being future-ready. FPGAs, especially those that intrinsically support BMCDR, are an advantageous choice to serve the rapid locking and recovery scheme and aid in reducing the cost of ownership and building early-to-market designs.

- Functional integration. Every designer hopes to develop a holistic solution with reduced cost of ownership using a single device that offers extended functionality with supplementary features. OLT system designers also expect a single solution that can accomplish the functions of a PHY and MAC while also performing packet processing, traffic management, and forward error correction, and in the context of NG-PON2, effectively execute BMCDR. FPGAs inherently offer system integration in a single device, and the latest generation includes FPGAs that offer additional characteristics tailored to support power-efficient small factor pluggable (SFP) modules while providing security and cryptographic functions, native IEEE 1588 integration, and BMCDR in diverse package sizes.

FPGA implementation requirements for OLTs

NG-PON2 (also known as TWDM-PON) is the second generation of passive optical network as defined by the ITU. It details an architecture capable of a total network throughput of 40 Gbps, corresponding to up to 10-Gbps symmetric upstream/downstream speeds available at each subscriber1 (Figure 2).

All the ONUs share the same upstream channel in a time-division multiplexed (TDM) fashion. The data thus shared by the ONU follows burst-mode transmission and is only sent during time slots allocated to it. Handling this burst data with inter-packet gaps proves to be a challenge for conventional CDR circuits with bang-bang phase detector phase-locked loops (PLLs) that cannot meet the stringent lock times required by the PON applications.

Oversampling provides an alternative solution to address this challenge for protocols supporting lower upstream data rates such as GPON (2.5 Gbps downstream/1 Gbps upstream) and XG-PON1 (10 Gbps downstream/2.4 Gbps upstream), albeit leading to higher power consumption. But at the 10-Gbps upstream speeds supported by the NG-PON2 protocol, oversampling becomes an infeasible solution for mid-density, mid-bandwidth-range FPGAs whose transceivers, until recently, have usually supported data rates up to a maximum of 12.7 Gbps.2

It therefore becomes critical for mid-range FPGAs used in NG-PON2-based OLT applications to feature native support for BMCDR circuitry on 10G transceivers. The CDR circuits in these transceivers are required for implementing fast and deterministic clock-data recovery, enabling the high-speed transceivers to stay in lock when there is no data present and resynchronize to the incoming data when the data is present on the receive serial lines.

Most FPGAs that are currently available with transceivers supporting native BMR circuitry belong to the high-end, expensive segment of the market. These FPGAs typically require larger footprints on the PCB and are optimized for superior performance at the expense of higher power dissipation. But a new class of mid-range FPGAs that are cost-optimized for OLT system applications solves these challenges in a small footprint (Figure 3). These devices feature a transceiver CDR circuit supporting BMR at 10G data rates. System designers can implement the NG-PON2 PHY layer on this type of FPGA because of its inclusion of hard transceiver IP blocks supporting CDR configurations using BMR. This FPGA approach also results in BOM cost savings, a smaller footprint, and greater functional integration.

Traditional OLT line card implementations do not operate under stringent low power-consumption requirements. However, newer applications like XFP modules with built-in OLT do require lower power dissipation, so FPGAs that service them need to be power-efficient. Devices based on non-volatile Flash/SONOS technology that feature transceivers architecturally optimized for mid-bandwidth applications provide the necessary power efficiency.

Security is another important issue. The implementation of proprietary OLT burst width and other vendor-specific information and protocols requires security of the user’s IP/bit-stream on the FPGAs. Additionally, many emerging PON applications such as smart grids and telemedicine, due to the confidential and sensitive nature of transmitted data, require advanced encryption processing, key exchange, and other data security features. It is imperative that FPGAs implementing PON-based OLTs provide best-in-class data and design security features.

FPGAs pave the way

A massive increase in bandwidth demand since the days of the first GPON/EPON installations has led to their TWDM-based successor NG-PON2 asserting its position as one of the key technological drivers for optical distribution networks of the future. While FPGAs offer many advantages for OLT designs, their use also comes with a few critical challenges. Cost-optimized FPGAs in the mid-density, mid-bandwidth range can address these challenges when they include integrated 10G transceivers supporting native BMR circuitry. These FPGAs enable OLT systems to meet the high data rate requirements and implementation flexibility of the NG-PON2 protocol, while also reducing BOM costs and delivering board space savings, lower power consumption, and critically necessary IP protection and data security.

Footnotes

[1] https://en.wikipedia.org/wiki/NG-PON2.

[2] Mid-range FPGA devices include Xilinx Vitrex5/6, Artix-7, Kintex-7 device families, Intel (Altera) Arria V, Cyclone V, 10 device families, Lattice ECP5 device family, and Microchip PolarFire device family.

References

- https://www.lightwaveonline.com/articles/print/volume-24/issue-10/technology/tech-trends/fpgas-follow-optical-industry-trends-53441377.html

- https://www.viavisolutions.com/de-de/literature/challenges-next-gen-pon-deployment-white-paper-en.pdf

- https://www.microsemi.com/document-portal/doc_view/136531-ug0677-polarfire-fpga-transceiver-user-guide

- https://www.microsemi.com/document-portal/doc_download/1243899-dg0841-polarfire-burst-mode-receiver

- https://www.sciencedirect.com/science/article/pii/S1084804516000989

Apurva Peri is senior engineer, FPGA product marketing, and Soumya Ganguly is engineer, FPGA product marketing, at Microchip Technology.