Segmentation-and-reassembly devices upgrade atm/Sonet networks

Segmentation-and-reassembly devices upgrade atm/Sonet networks

Single-chip segmentation-and-reassembly devices prove advantageous in several networking applications, including frame relay service interworking functions and local-area-network data packet conversion to Asynchronous Transfer Mode cells over fiber-optic networks

javier Berrios, transwitch corp.

Praveen goli, cascade communications

Next-generation segmentation-and-reassembly devices can serve as single-chip solutions for effective bandwidth management and source traffic shaping over Asynchronous Transfer Mode (atm) backbone networks at 155-Mbit/sec Synchronous Optical Network/Synchronous Digital Hierarchy (Sonet/sdh) transmission speeds. They can also integrate installed frame relay networks with atm networks for applications such as connecting legacy local area networks (lans).

The requirements for high levels of segmentation and reassembly dictate that very-large-scale-integration technology be used to future-proof atm networks. Such technology provides a migration path for accommodating changes and incorporating new features.

Incorporating an internal, programmable, reduced-instruction-set-computing (risc) processor within the segmentation-and-reassembly device to coordinate functions such as segmentation and reassembly, traffic shaping, or resource-management cell processing proves cost-effective and allows the inclusion of proprietary features by updating firmware rather than replacing hardware. As a result, devices can be upgraded quickly to meet rapidly changing standards requirements and ensure cost-effective, flexible design and high performance.

In addition, next-generation segmentation-and-reassembly devices should meet all International Telecommunication Union (itu), American National Standards Institute, and atm Forum specifications and possess built-in flexibility to adapt to customer changes. Single-chip solutions can incorporate a full Sonet/sdh framer, an integral peripheral-connection-interface (pci) bus, and direct-memory-access controllers, and require only external random access memory for most operations. Much of the functionality of the segmentation-and-reassembly device is defined by an executable code loaded in the internal risc processor. Traffic management complying with the atm Forum`s latest arbitrary-bit-rate specification is implemented in software.

To match high-speed atm/Sonet communications networking demands for flexible user bandwidth, present segmentation-and-reassembly devices provide throughput exceeding 155.52 Mbits/sec, and should be capable of handling a large number of simultaneous incoming and outgoing connections. The devices can also be used in applications such as hubs, routers, access switches, and network interface cards. On the horizon are experimental devices that can handle 622-Mbit/sec data rates.

Integration and conversion

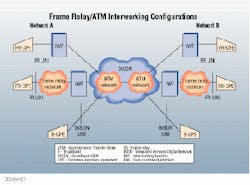

Single-chip segmentation-and-reassembly devices improve the integration of frame relay networks of T1 to T3 speeds and help convert lan data packets to atm cells over fiber-optic networks (see Fig. 1). The rates supported in both Sonet and sdh networks range from 51.84 Mbits/sec to more than 13 Gbits/sec, although the most common rate found in present access networks is 155 Mbits/sec.

Because of the rapid growth in Internet, intranet, and client/server applications, network designers are challenged to implement network systems that can function as required at a competitive cost. As backbones move to atm-based technology, one core function of these systems is the atm adaptation layer (aal), which couples or bridges the physical layer--Sonet and sdh technologies--with various applications.

As part of the aal, the segmentation-and-reassembly function provides the means of segmenting incoming data packets into fixed-length atm cells and then reassembling the cells back into packets. This function can be extended by adding service-specific layers that enable interworking to and from different networking technologies such as wide area networks and legacy lans. Two prominent applications of this type of technology are frame relay service-to-atm interworking and lan emulation.

Frame relay technology is widely used for virtual wide area networks. However, most of the backbone network is migrating toward an atm-based transport structure operating at 155 Mbits/sec or higher over Sonet/sdh fiber-optic systems. Because atm is a cell-based technology with a fixed length of 53 bytes per cell, its fixed-length configuration allows cell switching at higher speeds than is possible with variable- length packet switching schemes.

The atm structure also creates the opportunity to mix different types of traffic, such as voice, data, and video communications, into a single network. Due to the presently installed base of frame relay networks, however, it makes economic sense for network planners and providers to take advantage of the existing infrastructure by developing interworking solutions between frame relay networks and atm networks. In fact, itu-Recommendation I.555 specifies the interworking architecture between frame relay and atm networks in two applications:

Connection of two frame relay networks and customer premises equipment using Broadband Integrated Services Digital Network (bisdn) technology.

Connection of a frame relay network and customer premises equipment with a bisdn network and customer premises equipment using bisdn technology.

In these two applications, the interworking function between frame relay and atm networks uses a segmentation-and-reassembly device to segment and reassemble frames to and from cells. This function allows the interconnection of two frame relay-based entities through an atm-based network, which results in high-speed connections. In addition, this method supports many frame relay connections on the same backbone. The backbone interconnection is performed via fiber-optic channels with Sonet/sdh transport technology, typically at 155 Mbits/sec.

lan emulation

Another networking activity is the connecting of legacy lans to atm-based networks. In most installations, Ethernet switches are interconnected through atm networks to support a large number of Ethernet ports.

To interconnect legacy lans over atm networks, several characteristics of the lan networks must be emulated:

Connectionless services: Legacy lans do not establish a connection before sending the data. This approach departs markedly from the connection-oriented scheme in atm networks. Therefore, transparency must be provided in the emulated environment.

Multicast services: Legacy lans support broadcast/multicast communications. Two methods using atm-based networks can provide this capability: (1) intercept multicast/broadcast messages and forward them to the appropriate stations, or (2) send the messages to all stations and let the stations perform the filtering.

Interface control: Use a media-access-control driver interface in atm-based workstations.

Emulated lans: This requirement originates in the need for connecting independent lans into a single network. The atm network acts as a super-lan to which several lan segments are attached.

Interconnection with existing lans: Provides connectivity from atm stations to lan stations and from lan stations to lan stations across atm backbones.

According to the atm Forum`s document "lan Emulation 1.0," lan emulation can be used in two different configurations:

intermediate systems (routers, bridges) that enable communications between legacy lans over atm backbones,

end stations--hosts or personal computers--that enable communications between atm and lan stations.

For the latter configuration, high-performance segmentation-and-reassembly devices with lan emulation features are required for use over Sonet/sdh networks.

New features

New challenges for segmentation-and-reassembly devices include the push for a higher degree of integration. In particular, devices capable of aal processing, atm-layer functionality, and physical-layer functionality (for example, Sonet/sdh frame processing) are under development. Another is the ability of future devices to adapt to changing standards. This can be achieved by providing programmability in the device with an understanding that hardware and firmware functions must be well-balanced to deliver effective performance.

System solutions such as frame relay service or lan emulation represent only some of the requirements for segmentation-and-reassembly devices that serve high-speed optical networks. At the atm layer, traffic management is a key requirement, especially for available-bit-rate traffic and similar kinds of traffic. The ability to process resource-management cells to maintain the appropriate bandwidth allocation for available-bit-rate connections is an important feature that must be designed into a network to take advantage of advanced technologies such as atm. At the physical layer, it is necessary to provide interconnection to both private and public interfaces, namely, sts-3c/stm-1 frame processing and transparent asynchronous transmitter-receiver interfaces, respectively.

In general, hardware-intensive tasks such as physical-, atm-, and aal-layer functions are more efficiently performed in hardware. Higher-layer functions can be executed in software. An example of this is the Internet protocol over atm, in which protocol packets are segmented into aal type 5.

Programmability benefits

Advanced segmentation-and-reassembly devices must keep pace with continuously changing atm network requirements to allow customers to maintain standards-compliant solutions. For this reason, much of the core functionality of these devices should be contained as microcode in an internal risc processor. Using a risc-core approach with instruction code stored in random access memory allows new microcode to be loaded at any time, even after a device is installed in the field, without having to replace hardware. This flexibility ensures that devices can be kept current as standards evolve. In this way, customers receive updates faster than would be possible if device hardware changes were necessary or if the read-only-memory microcode required upgrading.

In addition to ensuring standards compliance, a major benefit of device programmability is the ability to incorporate application-specific features into risc microcode. Standard code supplied by vendors should meet the basic requirements for a segmentation-and-reassembly device, but an individual device might have various customer-specific modifications, providing product differentiation. Modifications or additions to the standard code can be made to perform virtually any function. Traffic-control algorithms for applications such as quantum flow control and low-jitter video segmentation are possible. Variations on aspects of signaling, session setup, performance monitoring, and other customer- specific functions can also be incorporated.

Device architecture

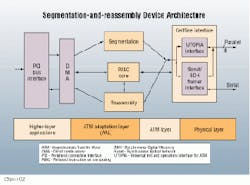

In a segmentation-and-reassembly device (see Fig. 2), the main functions include aal functions, atm-layer functions, and physical-layer functions such as Sonet/sdh and universal test and operations interface for atm, also known as utopia.

A pci to the host processor`s memory is desirable for lan packets that are being segmented or reassembled. A bus controller with direct memory access manages communications over the pci bus and provides a message communication link to the host processor. To ensure flexibility in supporting a range of applications, external, static random-access-memory chips are used to hold control information, load software, and act as buffers for incoming and outgoing cells. Special control functions included in the chip hardware are Sonet/sdh framing and overhead processing, input cell delineation and checking, output cell formatting, bidirectional communication control with host processor, and cell buffering through control memory.

Incorporating these functions into system hardware means that the programmable processor is available to respond to changing service demands for sequencing, prioritizing, and timing of outgoing cells, structuring routing for incoming cells, processing management functions to control traffic, interpretation of host processor requests and communication of results, and response to special maintenance and control requests. q

Javier Berrios is senior technical specialist with the systems group at TranSwitch Corp. in Shelton, CT (www.txc.com). Praveen Goli is senior network consultant with Cascade Communications in Westford, MA. He was formerly senior technical specialist with TranSwitch Corp.Fig. 2. For use in atm networks, a third-generation segmentation-and-reassembly device accommodates higher-layer applications, the aal, the atm layer, and the physical layer. Its main capability is the inclusion of direct interfaces and widely used system interconnections for physical- and atm-layer devices, such as universal test and operations interface for atm--also known as utopia--interfaces, or several parallel interfaces for medium-dependent layers--that is, optical/electrical interfaces.