Datacom and telecom approach 10G convergence

The release of the IEEE 802.3ae 10-Gigabit Ethernet (10-GbE) standard in August 2002 inspired much discussion about the convergence of data and voice networks. Such talk seemed appropriate because it was the first time data communications and telecommunications networks could operate at approximately the same standards-backed transmission rate.

At the same time, looking at the Open Systems Interconnection (OSI) reference model and the cross-reference table of market applications in Figure 1 illustrate, it became apparent that some convergence could occur at the physical layer. While this goal has proved challenging to achieve, avenues toward convergence have begun to appear.

Components normally found in the physical layer (PHY) of an optical communications system are optical-electrical (OE) and electrical-optical (EO) converters, analog ICs that drive and receive the optical signals, clock and data recovery (CDR), and a serializer/deserializer (SerDes) IC to provide a cleaner interface between the physical and datalink layers. In 10-Gbit/sec networks today, there is widespread use of 1.3-µm distributed feedback (DFB) and 1.55-µm electro-absorption DFB (EA-DFB) EO devices. Typically, these active devices are assembled into transmitter optical subassembly (TOSA) packages for ease of use by module and system designers.The subcomponents of the physical layer are typically partitioned at the TOSA, receiver-optical-subassembly (ROSA), and transceiver levels, which includes the TOSA/ROSA plus the analog ICs. At the 10-Gbit/sec level, it became necessary to integrate a SerDes into transceiver modules because host board designs and datalink-layer ICs were not prepared to deal with 10-Gbit/sec signals. The purpose of the SerDes is to supply a low-cost CMOS interface that can be routed over several inches of FR4 PCB material with manageable signal integrity and interoperability among all PHY ICs.

The majority of the 10-Gbit/sec market today is migrating toward integrated transceivers with SerDes or transceivers with CDR. Based on these trends, efforts have been made to converge on the PHY components used in datacom and telecom.

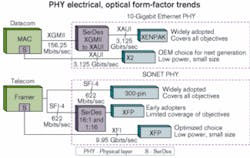

When OEMs began designing 10-GbE systems, the only readily available 10-Gbit/sec components were discrete/custom solutions and 300-pin modules. These discrete and module technologies were being used exclusively for SONET applications and had been shipping since early 2000. The 300-pin module was the industry’s first 10-Gbit/sec transceiver multisource agreement (MSA). Even though 10-GbE ran at 10.3125 Gbits/sec, slightly faster than SONET, the 300-pin-module technology was able to adapt. Thus, the first shipments of 10-GbE systems were made using 300-pin-module technology.

As 10-GbE evolved, however, OEMs in this space began to request features not supported by the 300-pin MSA. These new features included an SC receptacle, eight-port density on a typical Ethernet switch line card, hot-pluggable in the Z-direction, support for the new 10-Gigabit Attachment Unit Interface (XAUI) electrical interface, a single footprint for all reaches, and a management interface known as Management Data Input Output (MDIO). These features would enable attributes normally expected from Ethernet switches. The hot-pluggability provided an attractive business model for both system provider and end user alike. Pluggability offers flexibility and lowers the up-front costs of upgrading. Hot-pluggable modules enable systems to be shipped with partially populated or unpopulated ports that can be upgraded in the field without ever powering down the system. The premise is that the customer only pays for the bandwidth needed today and upgrades when business progress justifies the expense. This practice accelerates deployments of new standards by decreasing the investment needed for upgrading.

These advantages prompted the industry to develop a new MSA called XENPAK. In the early days of this development, members intended to support 10-GbE and SONET applications within the same form factor (i.e., convergence). The plan was to support the SerDes Framer Interface - Phase 2 (SFI-4 P2) and XAUI electrical interfaces that supported SONET and Ethernet applications. Both were four-wide electrical interfaces, so the form factor and electrical connector planned for XENPAK would easily accommodate each interface.

However, the two electrical interfaces were not compatible, which meant separate modules would still be necessary for SONET and Ethernet. An attempt was made to design a SerDes that supported Ethernet and SONET, but this came at a premium due to clocks, complexity, and further standardization support. The other main issue with convergence on XENPAK was the mechanical constraints it put on telecom-system designers. XENPAK required a cutout on the host board and needed to be front panel-mounted, both of which were difficult to implement in existing telecom chassis designs.

The limited availability of SFI-4 P2 IC technology and the mechanical burden of XENPAK hampered the market acceptance by telecom hardware engineers. From the datacom point of view, XENPAK was the perfect solution. XENPAK delivered flexibility and pluggability and supported all the required optical applications, which ranged from a few hundred meters on multimode fiber (MMF) to 80 km on singlemode fiber (SMF), including DWDM. Also, 10-GbE OEMs had invested heavily in XAUI technology, thus embedding the interface in datacom systems. XENPAK supported XAUI and became widely adopted for 10-GbE applications.

Telecom continued to use 300-pin and started to look at next generation packages. XENPAK and 300-pin are entrenched in their perspective markets and will survive a minimum of three to five years.

Meanwhile, OEMs began investing in next generation 10-Gbit/sec system designs. These modern system designs have more sophisticated software, higher throughput demands, less space for components, and in some cases less thermal capacity. XENPAK and 300-pin were too large for systems with these constraints. This shortcoming triggered industry participants to design a module optimized for these constrained systems.

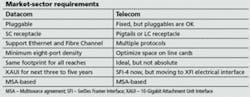

Before embarking on this effort, the minimum requirements for each market sector were studied. The MSA participants discovered that while some features began to converge key differences remained between each market sector (see Table). The datacom community supports Ethernet and Fibre Channel frames, selected XAUI as the next generation interface, and needs to support MMF and SMF. The telecom market requires support of a multitude of protocols, selected XFI as its future electrical interface, and primarily needs only SMF solutions. This divergence is understandable based on the network applications each market supports.There are several reasons a majority of datacom OEMs chose the X2 for next generation systems: low port cost, support of LX4 and CX4 IEEE-approved PMDs, commitment to XAUI, and higher confidence that long-reach optics and DWDM will be easier to accommodate in such a package. XFP added cost to each 10-GbE port because its design requires the SerDes function to be accommodated on the board; thus designers had to pay the SerDes costs up-front, regardless of whether the XFP slots were populated. While the additional cost may seem minimal, it conflicted with keeping port costs as low as possible. Keep in mind that is the prevailing interface in datacom; MACs with the XFI interfaces the XFP requires are still not widely available.

The other critical factor leading to X2 selection was support for the LX4 and CX4 PMDs. The LX4 and CX4 are important to 10-GbE OEMs because one supports the legacy MMF base and the other is a low-cost copper approach to 10-GbE. XFP does not support these PMDs.

Telecom OEMs selected XFP as their next generation form factor because it is protocol-agnostic (via the XFI) and compact and was regarded as a more “final” form factor for 10-Gbit/sec applications. X2 was viewed as an interim step, even though it could provide all the features they required.

The telecom market has not completely converted to XFP because not all reaches, including DWDM, are readily available. However, the shorter-reach supply base has made excellent progress, and there are multiple XFP suppliers. Thus, a combination of XFP and 300-pin exists today in most telecom systems. Some datacom-system vendors have followed a similar approach by designing XFP and XENPAK ports within the same system.

These hybrid approaches anticipate convergence upon the XFP may some day occur. For that to happen several factors must be addressed:

- XFP-compatible replacement for LX4. IEEE 802.3aq is developing 10GBase-LRM, which is intended to support legacy MMF. The expected release of the standard is early 2006.

- Low-cost copper version. IEEE 802.3an is developing 10GBase-T for copper. The expected release date of the standard is July 2006.

- Robust approach for DWDM and long-reach optics. Optimal designs will require new devices and packages (i.e., TOSA/ROSA).

- Framers and MACs with XFI interfaces. That, more than anything else, will accelerate wider acceptance of XFP or the next generation serial 10-Gbit/sec module.

The answer is yes-at the TOSA and ROSA level. However, it will take time. A variety of optical platforms were developed to support the 10-Gbit/sec form factor. As it turns out, focusing on the TOSA and ROSA for convergence can impact the economics of these modules. Based on historical data, the TOSA and ROSA account for about 70% of the cost of transceivers once they mature. Thus, leading laser suppliers created a common footprint for a 10-Gbit/sec TOSA. This platform could be used in all 10-Gbit/sec form factors and is known as the XMD uncooled TOSA MSA.

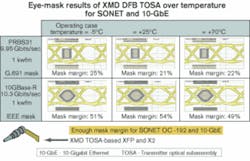

Figure 3 shows eye-mask results of an uncooled XMD TOSA in an XFP SONET application and X2 10-GbE application. The XMD TOSA meets both SONET and IEEE eye-mask specifications over the full operating-temperature range with sufficient margin. Eye-mask is just one parameter, but it is one of the best qualitative measures of transmitter performance.That is one example of convergence at the TOSA and ROSA level. Even though many tests will need to be performed to guarantee performance for both applications, much of this testing can be done during qualification and a smaller set of tests can be adopted for manufacturing screening purposes. Based on this success, efforts are being made to introduce a cooled version of the XMD MSA. Thus, convergence is occurring at the TOSA and ROSA levels.

Meanwhile, datacom OEMs have refocused their efforts on improving quality and reliability. Datacom modules are now as reliable as telecom modules, but remain at datacom prices. On the telecom side, there is a concerted effort to move away from discrete customized designs into MSA-based modules. The same quality is expected as before-but at datacom prices. One way to achieve this goal is via the XMD TOSA effort. Creating a common platform across all 10-Gbit/sec form factors will allow transceiver vendors to leverage volumes across all market segments, which will create near-equivalent costs for all the form factors. The transition to XMD will take time since that implies redesigns and re-qualification, but it will happen.

Transceiver manufacturers can expect continued reduction of power and size for 10-Gbit/sec modules. Figure 4 shows the power and size trends for the existing MSAs. The space inside transceivers for components is limited, and the smaller packages have less heat dissipation capabilities-a particular problem for long-reach transceivers that use 1.55-µm EA-DFB cooled or semi-cooled optics and packages. That’s why development of uncooled 1.55-µm EA-DFB technology for 40- and 80-km applications is critical. While this technology is in the early stages of development, the progress to date indicates that this device will become conducive to mass production. The advantages of uncooled 1.55-µm EA-DFBs include significant power savings and potential packaging into the XMD TOSA MSA.Another way to combat the poor thermal performance of these smaller packages is to increase the maximum transceiver operating case temperature from 70° to 85°C. That can only be achieved if the uncooled direct modulation DFB sources can sustain the higher junction temperature. Several advancements have been made in DFB technology that bring transceiver designers closer to higher operating case temperature. Looking even further down the road, there is optimism that long-wavelength VCSELs eventually will become economically producible in volume.

The ever-increasing demands on optics suppliers will not slow down. That makes it absolutely vital that transceiver manufacturers continue innovation of optoelectronic devices.

Edward Cornejo is director of product marketing at Opnext (Eatontown, NJ).