Effective synchronization designs for multiservice SONET equipment

Nino De Falcis, Datum Inc., and Hoshang Mulla and Bill Todd, TranSwitch Corp.

Synchronization of communications networks has long been taken for granted, but it is now becoming mission-critical for supporting the next generation of carrier-class, convergent multiservice networks. Maintaining proper synchronization of these complex new networks is a challenge for carriers. Synchronization traditionally has been located at the network core. As bandwidth demands escalate and carriers are required to support multiservice protocols such as ATM and Internet-protocol (IP) traffic over SONET, the need for robust synchronization is being driven lower and farther out into network topologies, even to the customer premises. Emerging broadband systems must work with the legacy public-switched telephone network (PSTN)-and that requires effective synchronization.Digital data in the public network must be transmitted and received at similar rates. The technology is sensitive to transmission impairments such as jitter and wander, especially at OC-3 and higher data rates. Jitter refers to phase error, or higher-frequency variations, caused by intervening network elements (NEs) that are regenerating or reconfiguring traffic. Wander, which refers to lower-frequency deviations, develops as a result of factors such as temperature variations in cables, phase quantization of slave clocks containing narrowband filters, and the cumulative waiting time effects of asynchronous multiplexers. Jitter and wander accumulate as signals pass through the network and may require regeneration of the synchronization reference signal to maintain data integrity, consistent equipment behavior, and adequate network performance.

The PSTN has developed techniques for "cleaning up" or reducing the impact of jitter, wander, and phase transients through the concept of building integrated timing supply (BITS), also known as the BITS clock. BITS designates only one clock as the synchronization source within a central office, major transport node, or network-edge equipment location. The BITS clock is the only clock permitted to receive a timing signal from outside the office. BITS concepts, which ensure the network maintains traceability to a Stratum 1 (highest-quality) primary reference timing source, are what keep today's PSTN synchronized.

As converged networks evolve to become more of a multivendor transport and delivery environment, maintaining standardized timing will be critical. Timing is an important network consideration for any carrier in terms of service capability, cost, and fast time-to-market for solutions. New carrier en trants, in particular, must quickly implement synchronization solutions that are cost-effective and tailored to their network timing needs.

What exactly is synchronization? For a digital-transmission circuit to operate correctly, the destination NE must receive data (bits) at the same rate as the source NE transmits them. In a communications network connecting several independent sources and destinations via transmission paths that are multiplexed, switched, and routed, synchronization is achieved by distributing a reference signal to every source, destination, and intermediate NE.

Until the mid-1980s, all U.S. carriers received their timing from one source-AT&T in Hillsboro, MO. In this hierarchical or "master/slave" scheme, time was distributed over a DS-1 signal through asynchronous networks. After the divestiture of the Bell System, the regional Bell operating companies (RBOCs) and other carriers had to secure their own timing sources. Private-enterprise systems such as wide-area-network (WAN) equipment extracted timing information from the received bit stream (i.e., loop timing) transmitted by public-network carriers.

Synchronization is established by deploying clocks throughout a network, with the local clock set to the same frequency as the clock where the transmission originated. Synchronization networks are normally designed with Stratum 1 clocks installed in major switching centers. These clocks are known as primary reference sources (PRSs). They utilize highly accurate timing devices based on a Cesium or global-positioning-system (GPS) standard. Another highly reliable PRS-traceable method is through code-division multiple access (CDMA) systems. Universal coordinated time (UTC), considered the standard for international time, is distributed by these networks using signals from 24 GPS satellites orbiting Earth every 12 hours.

Today's legacy networks are based on a hierarchical timing scheme incorporating different accuracy levels, or strata, of clocks. The American National Standards Institute (ANSI) standard for a Stratum 1 clock is an accuracy of ±1x10-11 (or 1 sec over 3,215 years) traceable to UTC. Stratum 1 clocks maintain the highest possible accuracy and stability. Stratum 2 and lower-level clocks are specified in terms of free-run accuracy and holdover performance. Free-run accuracy refers to the clock performance without any external references such as T1 span lines or GPS. Holdover is the performance of a clock that has lost its external timing reference and is using stored data acquired during normal operation to control its output frequency.These legacy networks are designed with high-performance clocks (Stratum 1 or 2) within the core of the network, providing traceable reference to lower-accuracy clocks (Strata 3/3E/4) at the edge of the network. Timing signal generators (TSGs), which provide holdover, are rated Stratum 2 or below. In the PSTN, they work in conjunction with distributed timing signals that are traceable to a PRS to maintain timing in the public network. They are the link to the outside world in that they are the only clocks that can receive a timing signal that originates outside the office. DS-1 signals distribute PRS timing throughout the network. TSG/BITS recovers the qualified timing source from these DS-1 signals, cleans it, provides Stratum 2E, 2, 3E, or 3 holdover in case of loss of all external timing sources, and distributes the qualified source in the central office. The widespread deployment of SONET makes this timing distribution scheme difficult. In particular, DS-1s that are carried over SONET are unsuitable as synchronization reference signals.

As the network infrastructure evolves and synchronization moves toward the edge of SONET networks, more Stratum 1 PRSs are being deployed across the network to feed TSGs instead of maintaining timing exclusively by means of a TSG or BITS clock. The advantage of this arrangement is that it greatly simplifies PRS traceability. Figures 1a and 1b illustrate this transition known as "flattening" the synchronization network.

Due to the critical importance of synchronization to network operation, the highest possible reliability is required. This reliability is obtained by using redundant clock sources and distribution paths. Redundancy of source, distribution, and the type of local NE must be considered when designing a synchronization network. A backup source is especially critical for widely distributed environments, high-traffic systems, mission-critical applications, and networks with data links of questionable reliability.

Local-exchange carriers (LECs) are deploying SONET as ring topologies in their networks to build high-capacity, reliable transport for delivering emerging services. Previously, these local carriers used asynchronous DS-1 signals from the interexchange carriers to provide their network timing. However, availability of GPS standards has given them their own affordable, PRS-traceable SONET timing source, making them independent of these carriers.Since SONET typically operates at higher data rates and with greater reliability, it demands improved synchronization capabilities, including better short-term stability, greater overall accuracy, and significant network-management capabilities, including synchronization status messages (SSMs). SSMs are clock-level identifiers (e.g., Stratum 1, 2, 3, or 4) embedded within the SONET overhead protocol reference signals used for traceability of clock sources for TSGs and other NEs. SSMs are transported between nodes in the SONET frame overhead and are often used in a closed loop to provide status of the timing signal. These messages prevent timing loops within the SONET ring. Timing loops will not generate alarms, but they will cause retiming buffer overflow or underflow conditions. SSMs are used to dynamically reconfigure the network to the best available Stratum-level timing scheme.

The flexible and reliable architecture of a SONET system necessitates a dynamic ability to rearrange and restore synchronization in a semi-automatic, near-real-time mode. Network designers must supply a stable, reliable frequency source that provides synchronization reference signals to drive high-speed digital communications.

In the era of asynchronous networks, timing offsets were handled by large buffers that slipped occasionally. However, synchronization capabilities were not as critical since data rates and overall percentage of data traffic in the network were low. Timing slips did not substantially impact network performance. Buffering is the ability to store and forward information on a short-term basis and is used to mitigate jitter and wander accumulation.

Figure 2 illustrates the concept of slip-control synchronization with an in-traffic write clock and out-traffic read clock. A slip buffer accommodates slight variations in frequency or phase by buffering the data before it is read out. Buffer size is a function of the expected amount of jitter and wander and the data transfer rate. If the in/out clocks are not adequately synchronized, phase variations exceeding the size of the buffer and frequency offsets will cause an overflow or underflow (slip) of the buffer, resulting in degradation of the output signal and data loss. A slip results in dropping or repeating a frame of data.

The impact of a slip depends on the type of traffic affected. For voice, a slip may be unnoticeable or cause only a clicking sound. Digital data requires retransmission if a buffer overflow or underflow occurs. For legacy applications such as analog modem and fax, slips have more serious consequences. A slip during a fax transmission, for example, would typically result in a missing line at the receiver. For analog data transmitted via modem, a slip could cause a modem problem that requires several seconds to resolve.

An asynchronous network combines low-speed signals into high-speed signals using multiplexing/demultiplexing methods. Variations in phase and frequency of low-speed signals caused by clock inaccuracy, jitter, or wander are accommodated by a technique known as "bit stuffing." SONET, however, maps and demaps digital DS-1 signals into STS-N electrical or OC-N optical signals. Due to the high capacity of SONET signals, a different accommodation technique is used. The STS-N payload and virtual-tributary (DS-1 container) pointers provide a mechanism to allow flexible and dynamic realignment of the payload within the SONET frame.Periodic adjustment of the pointers (pointer movement) is an elegant and efficient method for accommodating differences between the asynchronous and SONET clock rates. But it comes at a cost. Because of this mechanism, a DS-1 signal contained in the SONET payload can no longer be used to distribute timing over the network unless it meets the stringent maximum-time-interval-error (MTIE) requirements. Each pointer adjustment causes the DS-1 signal on the optical line to abruptly shift by 8 bits (1 byte), creating a phase transient of about 5 microsecs (see Figure 3). Because SONET pointer adjustments can degrade the timing quality of outbound asynchronous data, standards bodies are discouraging the use of SONET-carried DS-1

signals for timing-reference distribution. This development has made the network-planning process for distributing synchronization much more difficult.

An effective means of delivering timing and synchronization to a SONET network is by using STS frame signals for timing distribution. Timing distribution across the network can be achieved by deriving a DS-1 whose frequency is based on the received optical line rate. Since these timing references have no pointer adjustments, they do not adversely affect network timing quality.

Well-designed network-equipment clocks and timing distribution should be able to support the following critical rules to achieve optimal carrier-class network synchronization:

- Stratum 1 PRS traceability is a must to maintain accuracy and stability.

- Wander filtering should be performed using a frequency-lock-loop (FLL) device rather than a traditional phase lock loop (PLL).

- Phase build-out-removal of phase transients-must be implemented to mitigate cascading phase changes to downstream networks.

- Sufficient holdover must be provisioned to allow reasonable time for servicing before timing impairments are incurred.

- Input reference qualification is required to meet QoS performance requirements.

Qualification criteria should be based on the following performance and clock features:

- Timing accuracy/frequency errors-measurements of phase accumulation over time.

- Timing stability errors-definable MTIE threshold (worst-case real-time phase stability) and definable time-deviation (TDEV) threshold (statistical average of wander and phase stability).

- Source traceability errors-SSM at Stratum 1, 2, 3E, 3, and 4.

- Standard telecom signal errors-alarm indicator signal, out of frame, loss of signal, and bipolar violation.

- Minimum rearrangement or switchover MTIE is required.

- Planning for survivability to maintain minimum functionality during multiple fault scenarios is a must.

- Clock redundancy with no phase hit during switchover may be implemented, depending on the application.

- Performance monitoring of the synchronization signals should also be provided as a standard embedded offering in timing systems to ensure the best possible performance.

Since synchronization is fast becoming a customer-driven requirement for network OEMs, NE vendors are outsourcing non-core synchronization expertise to meet these requirements quickly and cost-effectively.

In the current business climate, when many companies are choosing to focus on their core competencies and technologies, there is little in-house synchronization and VLSI design expertise for developing cost-effective solutions. Reducing time-to-market is a major driver-and a proven third-party solution can speed time to market while reducing technical risk and staffing costs with off-the-shelf designs and technology. An NE designer must be able to add service value with product features, port density, and availability that maximize revenue potential and deliver reduced footprint, power requirements, and defects that minimize the cost of ownership.

Benefits of outsourcing synchronization systems design to manufacturers specializing in the discipline include obtaining best-in-class system performance, filtering algorithms, input reference qualification, performance monitoring, phase transient suppression, en hanced holdover, frequency synthesis, consistent behavior across product lines, and maintaining selective reuse of design. Outsourcing the development of non-core synchronization technology can help OEMs meet business and technical goals effectively.

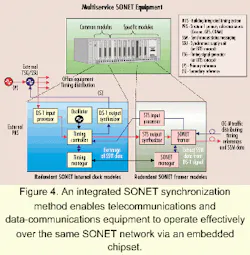

Since DS-1 signals transported over SONET can no longer be considered suitable timing distribution references due to the problems created by pointer adjustments, timing and synchronization product vendors and high-speed communications IC providers are developing integrated SONET devices to fill this gap and provide complete SONET synchronization management. These suppliers have shrunk standard synchronization technology onto a chipset to bridge the synchronization gap between telecommunications and data-communications equipment and create embedded equipment synchronization solutions.

Figure 4 illustrates an integrated SONET synchronization strategy. If an external PRS is present in an office, the stable STS clock signal within the SONET framer is used as a secondary timing reference. The STS clock signal does not suffer from phase transients or the detrimental effects of pointer adjustments. The SONET clock device within the equipment uses one or more STS clock sources as well as other available reference sources such as an external TSG or PRS to produce a single, accurate, stable reference signal distributed to all subsystems within the equipment that need a clock reference.

The SONET clock device may include components such as an STS input processor that converts the STS signal to a common 8-kHz timing reference signal; a local oscillator that provides a Stratum 3 or 3E holdover source in the event of loss of external reference; a timing controller that measures, qualifies, and selects from multiple input references based on standard synchronization requirements; a DS-1 output synthesizer that creates a stable DS-1 signal for an external TSG or BITS clock; and a DS-1 input processor to convert an external DS-1 signal into an 8-kHz reference signal. SSMs derived from the DS-1 signal contained in the SONET payload are exchanged between the SONET and timing managers to monitor the traceability of clock sources to avoid hard-to-detect timing loops, which degrade service quality. SSMs also allow dynamic rearrangements of timing when transmission faults occur.

The benefits of integrated SONET synchronization systems versus traditional systems include:

- The SONET network does not rely on potentially unstable and/or inaccurate DS-1 signals carried in the SONET payload for timing reference distribution.

- Robust implementation of self-healing, fully bidirectional timing networks. Not only are SONET networks bidirectionally self-survivable, but also the timing reference signal is routed redundantly.

- Embedded synchronization solutions provide full control and management of timing quality to ensure consistent equipment behavior that is critical for network performance and QoS.

- Embedded synchronization solutions provide the added feature of continuity for the SSMs exchanged between the SONET overhead bytes and the derived DS-1 reference signal, thus preserving the benefits of PRS traceability.

Embedded synchronization solutions are available as a family of software-configurable chipsets that datacom and telecom OEMs can use to build timing and synchronization capabilities into their equipment. These solutions deliver scalable synchronization functionality. Timing suppliers are working with carrier equipment vendors to embed synchronization technology in systems ranging from Class 5 switches to edge and access routers. Installing timing devices within multiservice switches increases efficiency for the customer.

Intelligent synchronization chipsets combined with innovative programmable SONET VLSI devices provide off-the-shelf design solutions for creating powerful synchronization implementations, enabling network communications equipment to support carrier-class transmission. Embedded scalable chipset offerings enable OEMs to significantly improve their time-to-market, shrink product size, and minimize design risks while containing costs.

Nino De Falcis is director of marketing communications at Datum Inc. (Austin, TX). Hoshang Mulla is director of marketing and Bill Todd is technical director, strategic applications, at TranSwitch Corp. (Shelton, CT).