PMC-Sierra's CHESS set extends SONET across the board

By Robert Pease

COMPONENTSPMC-Sierra is extending its penetration into optical-network-equipment architectures with the intro duction of a new OC-48/ OC48c (2.5-Gbit/ sec) channelized architecture to enable a new generation of integrated, carrier-class, multiservice networks. The Channelizer Engine for SONET/ SDH, or CHESS, chipset is designed to provide the foundation for convergence of voice and data infrastructures. The chipset extends SONET capabilities and increases bandwidth utilization so multiple formats can be carried over a single OC-48 optical interface.

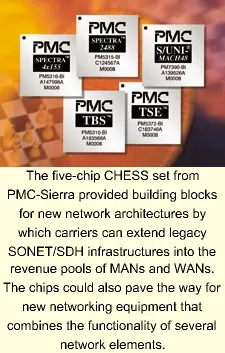

The CHESS chipset consists of five individual devices that operate together to allow Internet-protocol (IP) routing, ATM/frame-relay switching, SONET/SDH digital crossconnect and add/drop multiplexing, and DWDM transport functionality to be built in a single platform.

The PM5315 SPECTRA-2488 is an OC-48 or quad OC-12 channelized SONET/ SDH framer that performs section and line termination, as well as optional path termination down to STS-1 granularity. This chip also includes a timeslot interchange for grooming traffic down to an STS-1 level.

The PM5316 SPECTRA-4x155 is a quad OC-3 channelized SONET/SDH framer. It also integrates the complete clock and data recovery, clock synthesis, and serializer/deserializer functions.

The PM5310 TelcomBus Serializer (TBS) serializes and deserializes each of four 8x77.76-MHz TelecomBus data paths to 8b/10b encoded STS-12 serial links. The encoding enables optical backplane performance and provides in-band processing signals.

The PM5372 Transmission Switch Element (TSE) is a scalable 40-Gbit/sec STS-1 crossconnect device. Multiple TSE devices can be tiled to build single-stage fabrics from 40 Gbits/sec to 160 Gbits/sec and three-stage fabrics well into the terabit-capacity range.

The PM7390 S/UNI-MACH48 provides channelized ATM and packet mapping/delineation for an STS-48/STM-16 equivalent of bandwidth. This device allows a complete, arbitrary mix of multiservice traffic to an OC-48 aggregate of bandwidth.

"We believe this opens up a revolutionary new way to build Internet infrastructure equipment," says Steve Perna, vice president and general manager of PMC-Sierra's optical-networking division. "We have a lot riding on it, we believe the industry has a lot riding on it, and we know our customers have a lot riding on it."The chipset is designed to process SONET/SDH traffic carrying a variety of services, including IP, ATM, and time-division multiplexing. The CHESS architecture enables like traffic to be groomed to appropriate service-processing cards. For example, ATM traffic from an OC-48 optical interface can be groomed at STS-1 (52-Mbit/ sec) granularity to an ATM processing card, and IP traffic from the same interface can be groomed to a packet-processing card. Other features of the CHESS chipset architecture include line and service card and crossconnect fabric protection and channelization to even further granularity, down to DS-0 (64 kbits/sec).

Because the chipset consists of flexible modular components, system designers can develop unique architectures. CHESS interoperates with a host of other devices for complete architecture implementations. Carriers and Internet service providers (ISPs) can provision a greater number of services at less cost, as their system suppliers use the CHESS chipset to replace as many as five or six older, discrete network equipment elements.

This chipset can provide an immediate upgrade path for metropolitan area networks (MANs) and edge wide area networks (WANs), from OC-3 (155 Mbits/sec) to OC-48 and beyond. PMC-Sierra views the edge of the network as a substantial challenge in terms of network management. MAN and edge-WAN networks must not only aggregate the multiprotocol, low or multirate traffic from access customer-premises regions, but are also required to aggregate the wavelength base rate of OC-48/OC-48c traffic from native DWDM transport networks.

That makes it necessary to manage and groom SONET/SDH traffic at both the base access-rate and the base DWDM-rate granularities. The CHESS chips boast a first in the industry to provide capability for such dual-rate SONET/SDH grooming capability. The STS-1 grooming capability, in particular, will allow for sub-lambda processing so multiple user services can be run over individual OC-48 wavelengths. That solves the optimal lambda utilization problem of provisioning more than a single user service per lambda and will help enable the creation of new multiservice optical equipment classes, such as the integration of crossconnects, add/drop multiplexers, and switches.

"PMC-Sierra's new chips will help facilitate the upgrade of SONET networks that today use rates of only OC-3 and OC-12 and where bandwidth is still under-utilized due to the manual nature of provisioning and grooming SONET equipment," says Steve Byars of Current Analysis Inc., a Virginia-based telecommunications research and analysis firm. "More importantly, their channelization and crossconnect features will enable new equipment architectures where STS-1 bandwidth slices can be dynamically connected to processor engines for the appropriate service type. That will result in platforms where OC-48 interfaces are flexibly and efficiently utilized for a mixture of traffic types."

The company claims the majority of hardware functions are embedded in its silicon, thereby minimizing the investment in hardware design.